|

|

|

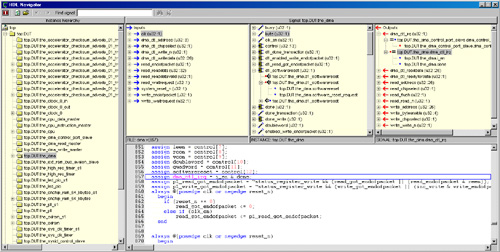

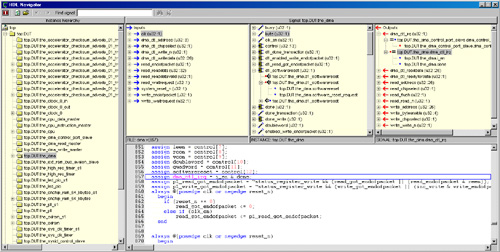

The HDL Navigator is extremely helpful to understand and debug HDL designs.

The HDL Navigator is a dedicated HDL browser, which uses both the source code and the compiled result. For each signal the

origin(s) and destination(s) can easily be traced in the browser.

It provides full visibility, including current values of parameters and uses different icons to indicate wires,

flip-flops, blocking assign, ...

Questions like: "What is the value of this parameter or generic in this

instance?" or "Which signals contribute to the

generation of this signal?" or "Which are all the

destinations of this signal?" are directly answered by

the HDL Navigator.

The icons used in the HDL Navigator immediately indicate

the type of the signal (wire, register, memory, ...) or

the usage of the signal (blocking assignment left hand

side used or right hand side used, used in a conditional

expression, used as a parameter, ...). After selecting

the signal the source code is immediately shown. This

provides a quick overview of where and how the signal is

used in the design.

A signal is often renamed when it

passes a module instantiation or when it is used in an

assign statement. Using tools such as 'grep' finds these

locations and then you normally 'grep' for the new

signal name to trace it further. The HDL Navigator uses

the compiled result and is aware of which signals are

actually the same wire. The HDL Navigator will trace the

real wire, which provides immediately a correct

overview of the usage.

The HDL Navigator Window

includes:

source

tree,

source

tree,

input

signals,

input

signals,

internal

signals,

internal

signals,

output

signals,

output

signals,

source

code.

source

code.

You can use 'Find' with wildcards to search for

signals. |

|

|

|

|

|

|

|

Provides a fast and complete view of an (unknown) HDL

design

Provides a fast and complete view of an (unknown) HDL

design

Easy to use, simple and common sense user interface, no

settings required

Easy to use, simple and common sense user interface, no

settings required

Shows resolved parameter values

Shows resolved parameter values

Shows signal dependencies

Shows signal dependencies

Shows usage of signals (left hand expression, blocking,

constants, etc)

Shows usage of signals (left hand expression, blocking,

constants, etc)

Shows all the different names in the design hierarchy of

the same signal

Shows all the different names in the design hierarchy of

the same signal

Direct link to the waveform window

Direct link to the waveform window

Direct link to the simulator, shows current value of

selected signal

Direct link to the simulator, shows current value of

selected signal

Supports

Verilog IEEE Std 1364-1995 and IEEE

Std 1364-2001

Supports

Verilog IEEE Std 1364-1995 and IEEE

Std 1364-2001 |

|

|

<

back

|