|

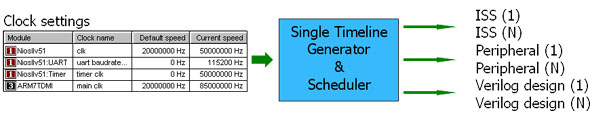

You can load many different modules

within Univers. Such modules are models of CPU's (ISSs),

peripherals, VHDL designs or Verilog designs. Each

module can have one or more independent clock inputs.

The clock frequency is specified in a window providing a

centralized overview of all clock signals.

The clock events, in combination with

other events, such as interrupts or signals between an

ISS and an HDL design, are correctly handled. Even clock

signals with nearly the same frequency (such as

clk1=20MHz, clk2=20.001MHz) are simulated correctly. A

single timeline generator and event scheduler with a

smart and highly effective proprietary algorithm is

responsible for best performance and exact clock

distribution, reflecting the real hardware in a

deterministic, reproducible, manner.

|