|

There is a need to boost the

software development to be able to deliver high quality

application code on time. Software development itself

becomes more complicated since a single processor system

will become rare in the future. Especially multi

processor systems require new development approaches.

Application development on a target board has advantages

and disadvantages. The major advantage is that the code

runs at the target speed. The disadvantages are not

neglectable, especially during the first phases of

product development. It is obvious that the target

hardware needs to be available for each software

engineer to allow short iteration cycles. A target can

be seen as a black box system which provides very

limited observability and controllability. By adding

costly HW recourses for verification purposes (break

units, trace buffers) this black box becomes at best a

gray box.

Evaluating

application code in a simulation environment where an

RTL simulator is also active is no solution. For a small

system an RTL simulation runs at a speed of

~200Hz. Assume the target

runs at 50MHz. This means the simulation environment

runs 250000 times slower. And software

engineers are not interested in waveforms but in

register views and in the current value of variables,

the frames on stack, etc.

A

well developed Instruction Set Simulators (ISS) runs at

a speed of several megahertz. When attention is paid to

the development of C++

peripheral models than it can

be statistically proved that they hardly influence the

simulation speed. Such a system is 10 times slower than

the target system, but fast enough to

boot a simulated OS and verify application code.

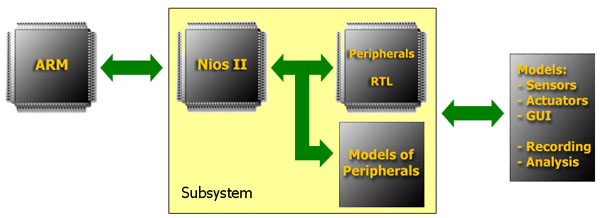

Univers fully supports the development and verification

of multi processor systems. For application code

development and verification Instruction Set Simulators

combined with C++ models of peripherals result in a high

speed virtual system. Such a system provides full

visibility and controllability to the development team.

C++ peripheral models can be added to model the outside world of

the system, such as sensors, actuators and visualization

of LCD output.

Univers includes a high speed digital simulator (VHDL

and Verilog) to support driver development and HDL

module design. For smaller, dedicated pieces of

software, the combination of a real ISS with the real

hardware design leads to early detection of interface

omissions.

Univers

benefits regarding system design:

True multi core development and verification

(accurate) True multi core development and verification

(accurate)

Extremely good observability and controllability Extremely good observability and controllability

High speed High speed

Processor vendor and type independent Processor vendor and type independent

No need for costly target hardware

for each engineer

No need for costly target hardware

for each engineer

Software view of peripherals

Software view of peripherals

Models may include

possible connections to the

outside world

Models may include

possible connections to the

outside world

|